# SUGAHARA LAB.

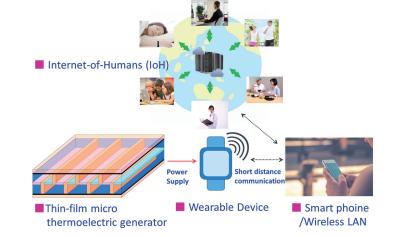

# Integrated Electronics for Ultralow-Power Edge/Wearable Computing and Internet-of-Humans

■ Beyond-CMOS devices/circuits ■ Micro thermoelectric generators CMOS Integrated circuits

FIRST, Imaging Science and Engineering Research Center

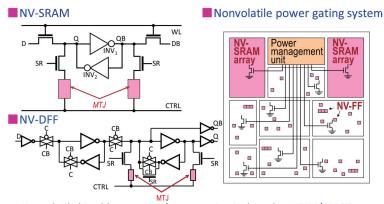

#### Low-standby-power CMOS logic technology using nonvolatile retention

- Nonvolatile bistable retention/memory circuits based on NVM/CMOS hybrid technology

- •Energy-efficient nonvolatile-power-gating architectures using nonvolatile

- NV-SRAM Macro CTRL buffer Row decoder Pre-charge Column decoder Readout/Write circuits

- •NV-SRAM → Highly effective at reducing standby power for caches

- •Applications: Microprocessors/Microcontroller and Processing-inmemory units (e.g. neural accelerator)

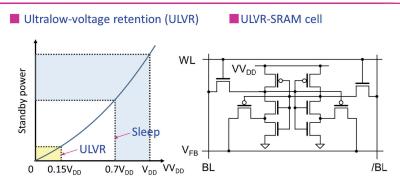

## Highly energy-efficient power-gating architecture based on ultralow-voltage retention

- •Conv. 6T-SARM: Sleep mode (0.7V<sub>DD</sub>) → Insufficient static power reduction

- ULVR-SRAM: ULVR at 0.15V<sub>DD</sub> → Highly efficient static power reduction -Normal inverter (NI) mode: High-performance operation at  $VV_{DD} = V_{DD}$ -Schmitt trigger (ST) mode: ULVR at  $VV_{DD} = 0.15V_{DD}$

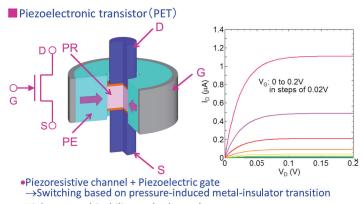

- Beyond-CMOS devices and circuits for ultralow-voltage high-speed logic systems

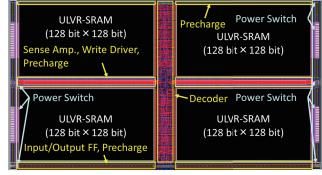

### 8kB ULVR-SRAM Macro

- ULVR-SRAM → Completely CMOS-compatible technology for highly efficient static power reduction

- Applications: Microprocessors, SoCs, and Processing-in-memory units (e.g. neural accelerator)

#### Micro thermoelectric generators using body heat for wearable devices

- •High current drivability at ultralow voltages

- Low leakage CMOS compatible circuits